FPGA学习:状态机化简&Testbench

FPGA学习 :状态机及其化简&Testbench

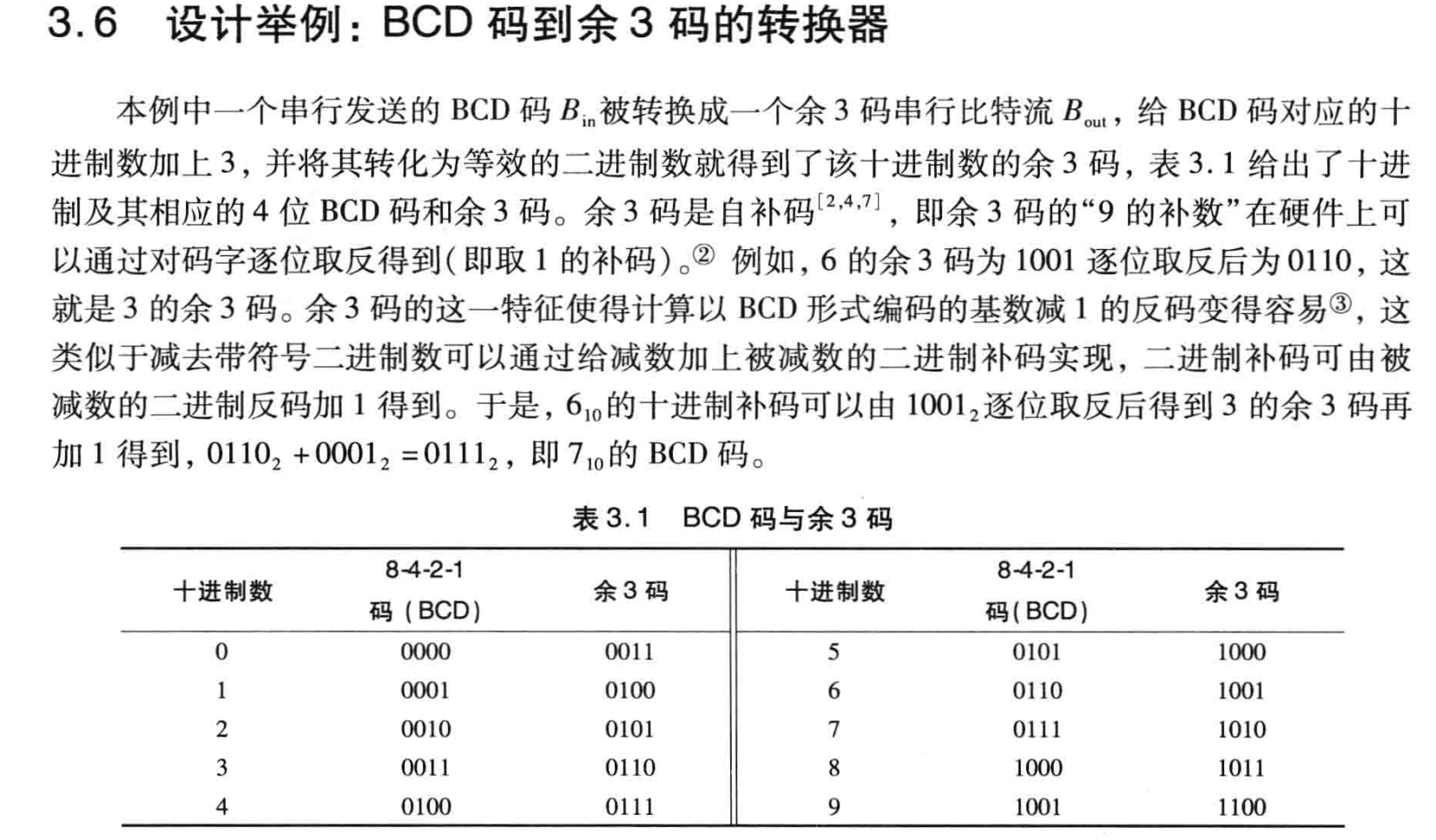

这里练习状态机利用《Verilog HDL高级数字设计》中的一个示例设计,该设计将从低位到高位串行输入的BCD码转换为从低位到高位串行输出的余三码,利用状态机判断每位的状态然后根据输入的数据判断输出数据。具体题目如下:  说句实话,这个题目有点为了用状态机而用状态机的意思了,要将串行输入BCD以余三码串行输出的方式我能想到的其实很简单,完全不需要状态机,用四个DFF做缓冲串转并,然后把转完的数加上0011即可,最后再用四个DFF并转串输出。 但是人家既然要求了要用状态机,那就做呗,顺便研究下状态机化简😅

说句实话,这个题目有点为了用状态机而用状态机的意思了,要将串行输入BCD以余三码串行输出的方式我能想到的其实很简单,完全不需要状态机,用四个DFF做缓冲串转并,然后把转完的数加上0011即可,最后再用四个DFF并转串输出。 但是人家既然要求了要用状态机,那就做呗,顺便研究下状态机化简😅