Renesas RE01B MCU Study Notes :Overview

这是一款基于Cortex-M0+的超低功耗MCU,但其实刚拿到文档的时候,它让我眼前一亮的并不是超低功耗这个关键词,而是它支持蓝牙5.0、具有2D加速的功能,也就是说这一块低功耗芯片片上就具有完整的无线通信协议栈,而不是像以前接触过的STMicro32那样。大胆预测一下,它应该是应用在长续航场景下的移动设备上,例如智能手环之类的。

这是一款基于Cortex-M0+的超低功耗MCU,但其实刚拿到文档的时候,它让我眼前一亮的并不是超低功耗这个关键词,而是它支持蓝牙5.0、具有2D加速的功能,也就是说这一块低功耗芯片片上就具有完整的无线通信协议栈,而不是像以前接触过的STMicro32那样。大胆预测一下,它应该是应用在长续航场景下的移动设备上,例如智能手环之类的。

参赛单位:武汉理工大学 队伍名称:木大木大 指导老师:钟毅,张家亮 参赛队员:甘云汉,陆国威,万禹壮 总决赛奖项:一等奖(ARM杯企业大奖)

“时钟域(clock domain)”可以说是数字集成电路中一个非常重要的内容了,那么,何谓“跨时钟域”?

很好理解,在时序逻辑电路中,所有触发器、寄存器的运行都是由时钟激励而运行下去的。而一个大型的数字系统中不可能只有一种时钟:

例如Cortex-M3软核常常运行在50~100MHz、而UART串行口波特率要在921600以上的话,输入时钟频率最好高于200MHz、FPGA上的DDR3一般要求200MHz的时钟输入,不同PLL/MMCM输出的同频率时钟它们的相位也有可能不同……

这么多不同时钟激励的系统要组合在一起并能进行数据交互,那么势必会遇到“跨时钟域”的问题,解决这个问题的一大方法之一就是利用异步FIFO进行数据交互

FIFO(First In First Out),顾名思义,即先输入先输出的一种模块,FIFO一般分为同步FIFO和异步FIFO两种,同步FIFO即输入和输出在同一个时钟域中,异步FIFO即输入输出不处于同一个时钟域。

FIFO的存储模块可以看成一个二维寄存器(当然也可以通过生成ram代替),因此有些概念需要掌握,即:

作为AMBA的中流砥柱之一,AHB被用于高性能、高时钟频率的系统结构中,它多被用在ARM核与片内高速sram、flash、DMA和总线桥的连接。它和上次学到的APB的最大区别在于功能更加丰富,可以进行流水线操作,并且性能更强。

对于Split事务处理、多个Master的特性,这一篇就不写了,只讲讲最基础的数据传输以及流水线操作。更多细节可以查看AMBA5手册(ARM IHI 0033B.b

),本文中大量图片也来源于官方手册。

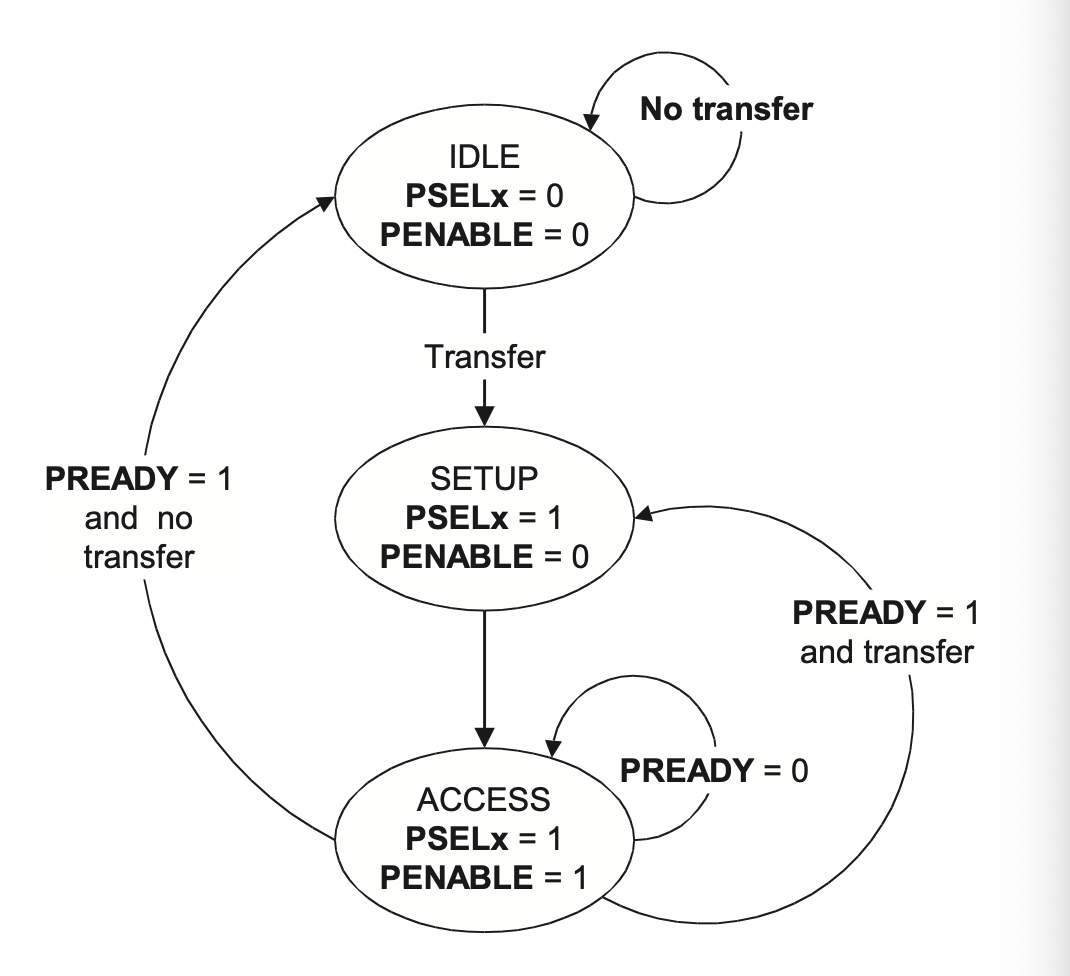

APB总线是AMBA里面最简单的一个总线接口了,它是一个非流水线结构,且控制逻辑简单,这也就决定了它是利用于低带宽的外围总线设备上,例如UART、IIC、定时器等等。注意,APB还有一个特点就是,APB的主机只有一个,那就是APB总线桥,不可能有其他主机,也不可能有多个主机。

APB总线接口的状态转换图如图所示(ARM IHI 0024B - Page3-2):

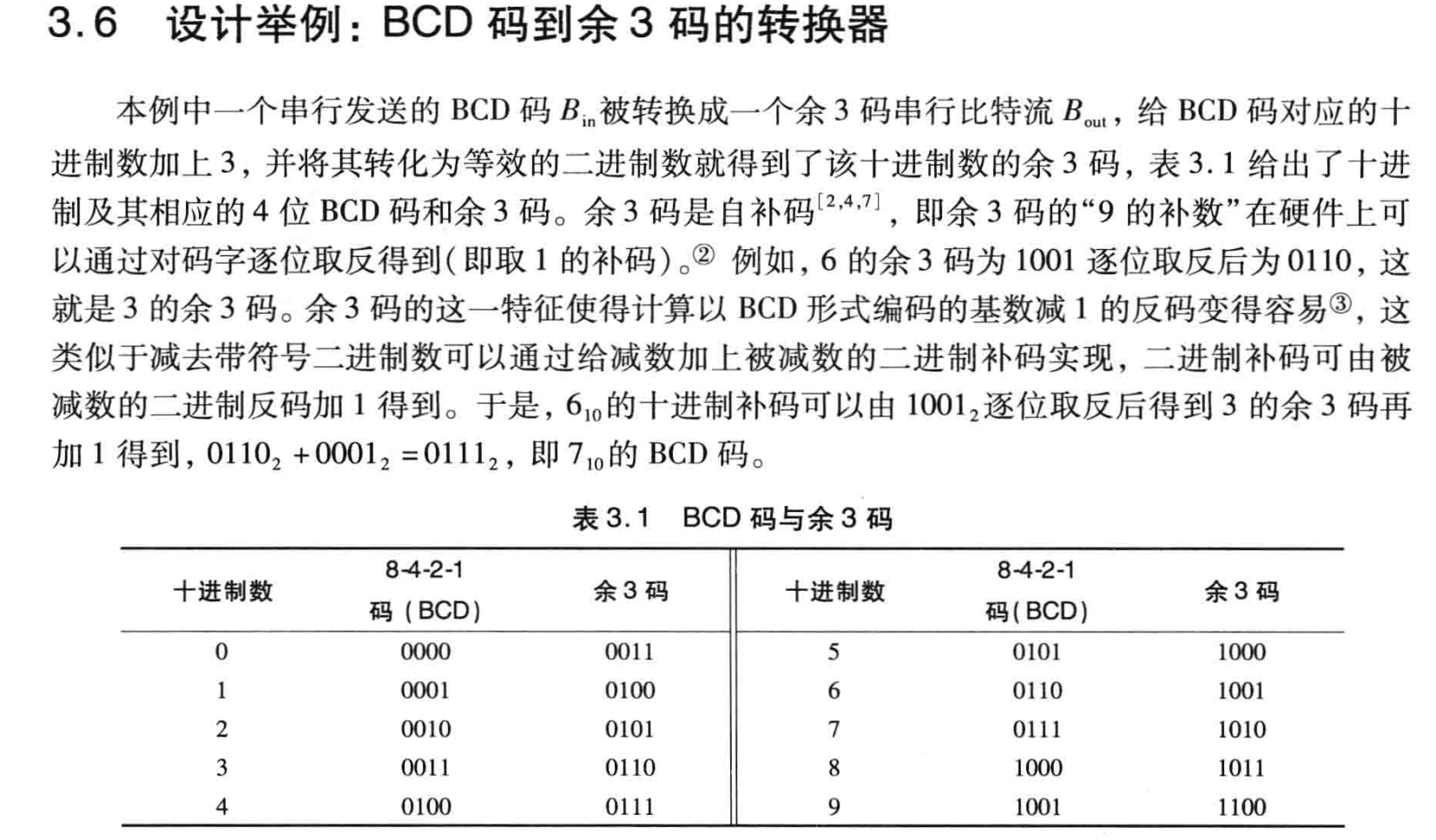

这里练习状态机利用《Verilog HDL高级数字设计》中的一个示例设计,该设计将从低位到高位串行输入的BCD码转换为从低位到高位串行输出的余三码,利用状态机判断每位的状态然后根据输入的数据判断输出数据。具体题目如下:  说句实话,这个题目有点为了用状态机而用状态机的意思了,要将串行输入BCD以余三码串行输出的方式我能想到的其实很简单,完全不需要状态机,用四个DFF做缓冲串转并,然后把转完的数加上0011即可,最后再用四个DFF并转串输出。 但是人家既然要求了要用状态机,那就做呗,顺便研究下状态机化简😅

说句实话,这个题目有点为了用状态机而用状态机的意思了,要将串行输入BCD以余三码串行输出的方式我能想到的其实很简单,完全不需要状态机,用四个DFF做缓冲串转并,然后把转完的数加上0011即可,最后再用四个DFF并转串输出。 但是人家既然要求了要用状态机,那就做呗,顺便研究下状态机化简😅

一年没更新了,过去的一年里一直忙着比赛和课业,一直没有更新博客里的内容,从今天开始再填完埋下的坑吧!

至于为什么会有这个奇怪的番外篇,是因为最近更新了装备,整了台X86的MacBook Pro,为了方便我写verilog和仿真看波形,整合了网上的很多教程最终写出来的。

这其中还包括利用yosys对写好的verilog进行综合的环节,但我想了下,在macOS下烧写fpga十分困难或者对我来说几乎不可能,因此我就虽然写了这部分教程,但我基本没用过综合,非要综合的话利用docker或者虚拟机安装vivado不香嘛😅

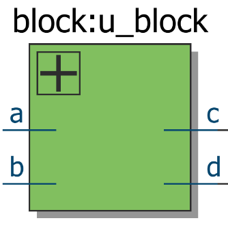

Verilog的基本设计单元是“模块”block,一部分描述接口,另一部分描述逻辑功能,比如: 1

2

3

4

5

6

7

8module block(a,b,c,d);

input a,b; //描述接口

output c,d;

assign c = a | b; //描述逻辑功能

assign d = a & b;

endmodulea,b,c,d

由于想学习FPGA的相关内容,同时给数字电路打点基础,于是借助着B站上西安电子科技大学的视频开始学习Verilog HDL这门硬件描述语言,在学完语言后,将按照**《FPGA设计技巧与案例开发详解》**这本书上的相关内容在一块核心为Altera Cyclone IV的开发板上完成基本例程,之后在网上寻找相关项目学习、开发

| 设备 | 数量 | 供电 | 控制方式 |

|---|---|---|---|

| 动力电机 | 2 | 24V供电 120W额定功率 | PWM+5V+方向IO+GND |

| 船方向舵机 | 2 | 24V供电 约 24W功率 | PWM+5V+GND x 2 |

| 迪文串口屏 | 1 | 5-15V供电 | 232电平串口通信 |

| mpu6050角度/加速度 | 1 | 3.3V供电 | I2C通信 |

| 气泵 | 1 | 12V供电 35W额定功率 | PWM占空比控制喷气量 |

| 电磁阀 | 1 | 12V电压 | 开关,常闭,继电器/MOS管控制 一个IO口 |

| 流量计 | 1 | 5V供电 | IO口测频率 |

| 移动配载平台 | 1 | 12V供电 约36W功率 | PWM + 5V+方向IO |

| 电流传感器 | 1 | 3.3V供电 | I2C通信 |

| WiFi通信 | 1 | 3.3V供电 | TTL串口通信 |

以上是气泡船预计所要接的全部外设,结合上述统计,分配供电,作出下列框图: